IC・トランジスタで出来たコンピューターを設計・製作するためのブログ

| Jeans & Development | 電子ブロック工房 | 三日坊主 | フロントページ |

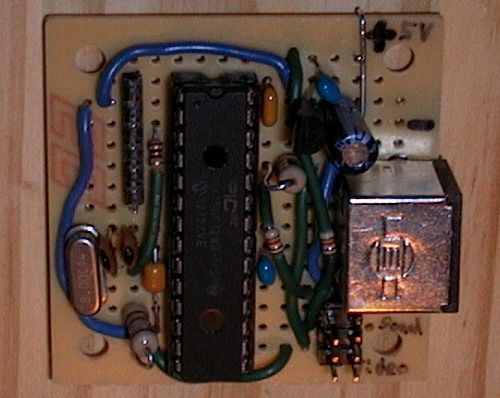

KM-Z80 mini version 0.3 [PIC]

2013年7月27日

PIC32MXを用いたMZ-80K互換機の3号機が完成し、ほぼ安定して動くようになった。なお、回路図及びPICプログラムが若干変更になり、ver 0.3としている。

表側は、こんな感じ。左から、電源スイッチ、パイロットランプ(カナの時は赤)、PS/2キーボードコネクタ、テープレコーダー(もしくはiPod)入力端子。

表側は、こんな感じ。左から、電源スイッチ、パイロットランプ(カナの時は赤)、PS/2キーボードコネクタ、テープレコーダー(もしくはiPod)入力端子。

オマケ: ZK-MIPS mini (TK-80風、MIPS32 トレーニングキット) [PIC]

2013年7月27日

ZK-80 miniではMIPS32 CPUを内蔵したPIC32MXに、8080 CPUをエミュレーションさせている。MIPS32を内蔵した石であれば、MIPS32のプログラムを動かせるだろうということで、作ってみた。MIPSの命令を、ハンドアセンブルできる人限定のツール(笑)。

ZK-80 mini (PIC32MXを使った1チップTK-80互換機) [PIC]

2013年7月10日

ZK-80 miniを紹介します。NECのTK-80互換機で、Microchip社のPIC32MX120F032Bを用いて1チップで構成されています。

KM-Z80 mini version 0.2 [PIC]

2013年6月15日

KM-Z80 mini は、Microship の PIC32MX150F128B を用いた、1チップのSHARP MZ-80K 互換マイコンです。

最初の正式バージョンとして、version 0.2 を公開します。

KM-Z80 mini version 0.2 のダウンロードはこちらから。

ライセンスは、私がソースコードを書いた部分は、LGPL v2です。ただし、CG-ROMとモニターROMに関する部分は別のライセンスになっているので、注意して下さい。これらのROMデーターを取得したMZ-700 Emulatorのサイトによると、KM-Z80 mini は「営利を目的としない限り自由」に使用可能なライセンスで配布可能だと理解しています。

最初の正式バージョンとして、version 0.2 を公開します。

KM-Z80 mini version 0.2 のダウンロードはこちらから。

ライセンスは、私がソースコードを書いた部分は、LGPL v2です。ただし、CG-ROMとモニターROMに関する部分は別のライセンスになっているので、注意して下さい。これらのROMデーターを取得したMZ-700 Emulatorのサイトによると、KM-Z80 mini は「営利を目的としない限り自由」に使用可能なライセンスで配布可能だと理解しています。

KM-Z80 mini + カセットテープインターフェース [PIC]

2013年6月10日

KM-Z80 mini version 0.182 [PIC]

2013年2月10日

最新のPIC32MX150F128Bの仕様では、Max Speed MHz が 50 になっている。以前は40 MHzであったので、KM-Z80 miniも40 MHzで動かしていた。

この1.25倍の速度の違いが、KM-Z80 miniの開発に於いては非常に大きい。と言うのはPIC32MXの実行速度が、MZ-80Kをエミュレートするのにぎりぎりであったからである。CPUのリソースのうち、4割ほどがビデオシグナルの作成に取られていたため、残りの6割しかZ80-CPUのエミュレーションに使えなかった。この状態で、速度調整のためのウェイトルーチンをいっさい入れなかった場合に、かろうじておおよそ2 MHzでZ80が動いていた。

PIC32MXが、今までの1.25倍の速度で動くと、Z80のエミュレーションは1.25倍どころか、もっと速くなる。と言うのは、ビデオシグナル作成も速くなるため、より多くの時間をZ80のエミュレーションに費やすことができるようになるからだ。

この1.25倍の速度の違いが、KM-Z80 miniの開発に於いては非常に大きい。と言うのはPIC32MXの実行速度が、MZ-80Kをエミュレートするのにぎりぎりであったからである。CPUのリソースのうち、4割ほどがビデオシグナルの作成に取られていたため、残りの6割しかZ80-CPUのエミュレーションに使えなかった。この状態で、速度調整のためのウェイトルーチンをいっさい入れなかった場合に、かろうじておおよそ2 MHzでZ80が動いていた。

PIC32MXが、今までの1.25倍の速度で動くと、Z80のエミュレーションは1.25倍どころか、もっと速くなる。と言うのは、ビデオシグナル作成も速くなるため、より多くの時間をZ80のエミュレーションに費やすことができるようになるからだ。

KM-Z80 mini α version [PIC]

2012年12月23日

KM-Z80 mini + keyboard [PIC]

2012年12月16日

4 bit RISC CPUの回路 [CPU]

2012年12月11日

KM-Z80 mini 進捗 [PIC]

2012年12月9日

32ビットPIC(PIC32MX150F128B)を用いた1チップMZ-80K互換マイコン作成の進捗状況。NTSCビデオ信号送出とZ80 CPUのエミュレーションまで完成し、モニタープログラムが起動するところまで来た。

現在、PS/2キーボードからの信号を処理する部分を書いている。これが済めば、とりあえずコンピューターの体を成すことになる。

現在、PS/2キーボードからの信号を処理する部分を書いている。これが済めば、とりあえずコンピューターの体を成すことになる。