IC・トランジスタで出来たコンピューターを設計・製作するためのブログ

| Jeans & Development | 電子ブロック工房 | 三日坊主 | フロントページ |

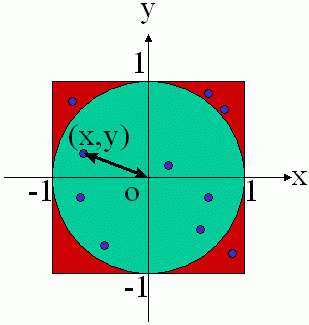

モンテカルロシミュレーションで円周率を求める [シミュレーション]

2007年4月29日

モンテカルロ法で円周率を求めるアルゴリズムはいたって簡単。-1 から 1 までの乱数を、x, y として用意し、図のように点(x,y)と座標の原点までの距離が1以下であれば円の内側だとみなされる。ピタゴラスの定理より、単に

x*x + y*y

の値が1より大きいか小さいかを求めればよい。これを何回も繰り返せば、円の内側に点が入る確率が求まる。その確率を p とすると、外側の正方形の面積が4であるから、円周率は次のように得られる。

π = 4 * p

とりあえずの目標:どんな計算をさせるか [一般的なこと]

2007年4月28日

さて、自作コンピューターが完成すればどのような計算をやらせるかを考えておく必要があるだろう。何をやらせるかを決めないと、設計図が仕上がらない。

簡単すぎてもいけないし、難しすぎてもいけない。例えば、2進数一桁の足し算をやらせるだけならば、簡単なデジタル回路を制作するだけでよい。逆に、今作ろうとしている自作コンピューターでインターネットに接続することは、ほとんど不可能である。絶対に不可能であるとは言わないが、最初の目標としては高すぎる。

その中間として、円周率を求めることを目標にしたい。アルゴリズムとしては、モンテカルロシミュレーションを用いる予定である。これには、精度の良い乱数と、乗算を求めるプログラムが必要である。

簡単すぎてもいけないし、難しすぎてもいけない。例えば、2進数一桁の足し算をやらせるだけならば、簡単なデジタル回路を制作するだけでよい。逆に、今作ろうとしている自作コンピューターでインターネットに接続することは、ほとんど不可能である。絶対に不可能であるとは言わないが、最初の目標としては高すぎる。

その中間として、円周率を求めることを目標にしたい。アルゴリズムとしては、モンテカルロシミュレーションを用いる予定である。これには、精度の良い乱数と、乗算を求めるプログラムが必要である。

ニーモニック表 [CPU]

2007年4月27日

演算命令

INC A

DEC A

INC B

DEC B

INC C

DEC C

COMP A,D

ADD A,D (結果は、Zレジスタに入る)

NOT A (結果は、Zレジスタに入る)

NOT D (結果は、Zレジスタに入る)

AND A,D (結果は、Zレジスタに入る)

OR A,D (結果は、Zレジスタに入る)

SHL A (上位ビットにCF2を使いシフト。下位ビットはCF1へ)

SHR A (下位ビットにCF2を使いシフト。上位ビットはCF1へ)

ジャンプ命令

JMP (ジャンプ先は、Jレジスタの値)

JZ (ジャンプ先は、Jレジスタの値)

JNZ (ジャンプ先は、Jレジスタの値)

JC (ジャンプ先は、Jレジスタの値)

JNC (ジャンプ先は、Jレジスタの値)

LOOP(ジャンプ先は、Jレジスタの値)

JMPF(MOV CS,Z 及び MOV IP,J)

INC A

DEC A

INC B

DEC B

INC C

DEC C

COMP A,D

ADD A,D (結果は、Zレジスタに入る)

NOT A (結果は、Zレジスタに入る)

NOT D (結果は、Zレジスタに入る)

AND A,D (結果は、Zレジスタに入る)

OR A,D (結果は、Zレジスタに入る)

SHL A (上位ビットにCF2を使いシフト。下位ビットはCF1へ)

SHR A (下位ビットにCF2を使いシフト。上位ビットはCF1へ)

ジャンプ命令

JMP (ジャンプ先は、Jレジスタの値)

JZ (ジャンプ先は、Jレジスタの値)

JNZ (ジャンプ先は、Jレジスタの値)

JC (ジャンプ先は、Jレジスタの値)

JNC (ジャンプ先は、Jレジスタの値)

LOOP(ジャンプ先は、Jレジスタの値)

JMPF(MOV CS,Z 及び MOV IP,J)

CPUのスペック案 [CPU]

2007年4月27日

レジスタは8ビット、メモリ空間の1ワードは4ビットの変則型にしようと思う。メモリ空間は、16ビットのアドレス指定で64Kワード(32Kビット)。CS・DSを用いたセグメント指定により、256ワードごとに空間を分割して使用する。

Aレジスタ(8ビット) - 演算用

上位4ビット:AHレジスタ

下位4ビット:ALレジスタ

Bレジスタ(8ビット) - メモリアドレス指定用

上位4ビット:BHレジスタ

下位4ビット:BLレジスタ

Cレジスタ(8ビット) - カウンタ

上位4ビット:CHレジスタ

下位4ビット:CLレジスタ

Dレジスタ(8ビット) - 演算補助

上位4ビット:DHレジスタ

下位4ビット:DLレジスタ

Jレジスタ(8ビット) - ジャンプ先指定

Zレジスタ(8ビット) - 代入および演算結果格納

上位4ビット:ZHレジスタ

下位4ビット:ZLレジスタ

Fレジスタ(4ビット) - フラグ格納用

CF1(キャリーフラグ)

CF2(シフト・ローテート用フラグ)???

ゼロフラグはない(Zレジスタがゼロフラグを兼ねる)

サインフラグはない(Zレジスタ上位1ビットがサインフラグを兼ねる)

IP(8ビット) - 命令実行位置

CS(8ビット) - コードセグメント

DS(8ビット) - データセグメント

最初の設計では、インテル型にしてみた。スタックの実装は、とりあえず先送りにする。

Aレジスタ(8ビット) - 演算用

上位4ビット:AHレジスタ

下位4ビット:ALレジスタ

Bレジスタ(8ビット) - メモリアドレス指定用

上位4ビット:BHレジスタ

下位4ビット:BLレジスタ

Cレジスタ(8ビット) - カウンタ

上位4ビット:CHレジスタ

下位4ビット:CLレジスタ

Dレジスタ(8ビット) - 演算補助

上位4ビット:DHレジスタ

下位4ビット:DLレジスタ

Jレジスタ(8ビット) - ジャンプ先指定

Zレジスタ(8ビット) - 代入および演算結果格納

上位4ビット:ZHレジスタ

下位4ビット:ZLレジスタ

Fレジスタ(4ビット) - フラグ格納用

CF1(キャリーフラグ)

CF2(シフト・ローテート用フラグ)???

ゼロフラグはない(Zレジスタがゼロフラグを兼ねる)

サインフラグはない(Zレジスタ上位1ビットがサインフラグを兼ねる)

IP(8ビット) - 命令実行位置

CS(8ビット) - コードセグメント

DS(8ビット) - データセグメント

最初の設計では、インテル型にしてみた。スタックの実装は、とりあえず先送りにする。

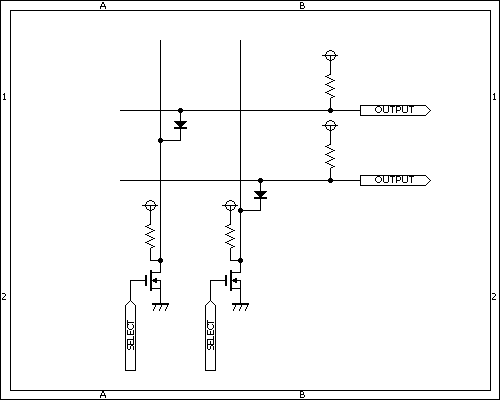

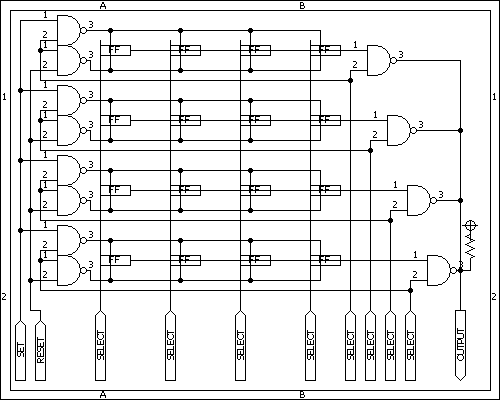

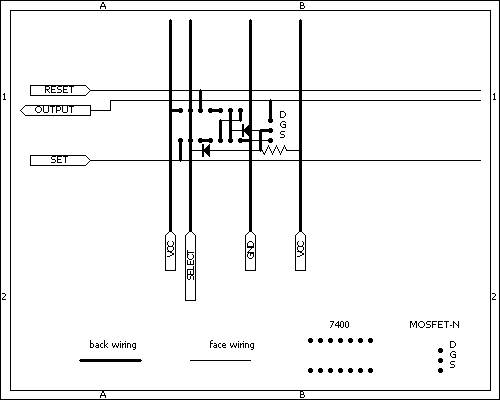

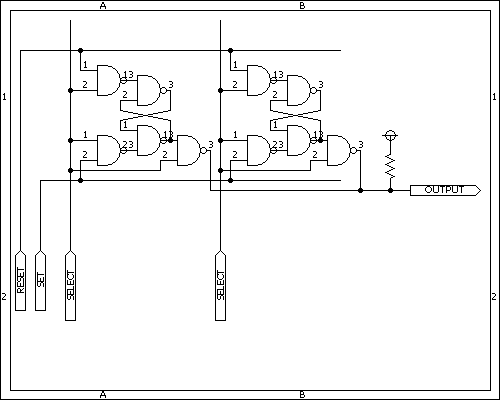

フリップフロップ [配線]

2007年4月27日

1ビットあたり、7400 を一つ、MOSFET を一つ、ダイオード2つ、抵抗を一つの設計。

この回路は、4/26の2つの回路の折衷案。フリップフロップ部分と入力の選択に7400を、出力の選択にMOSFETを用いている。

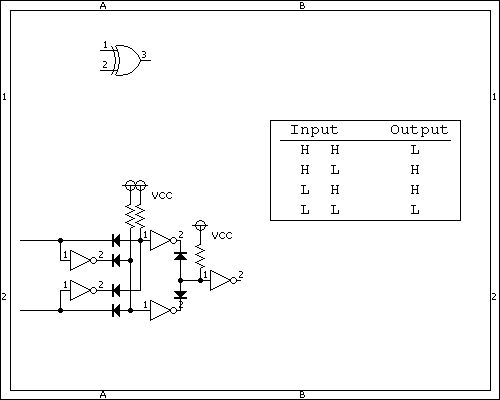

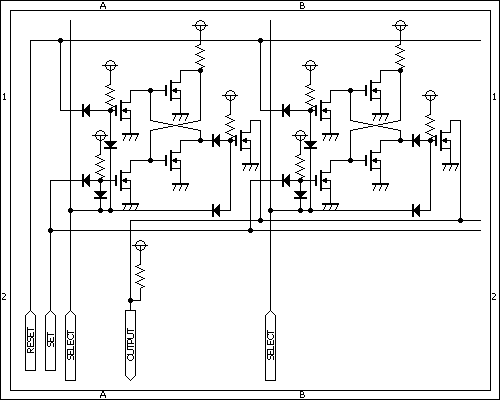

フリップフロップ [デジタル回路]

2007年4月25日

RAMの基本となる、記憶回路。記憶自体は2つのNANDで実現できるが、選択信号による接続・非接続の部分に3つのNANDが要りそう。再考の余地あり。

もしかしたらこの部分は、はじめからMOSFETで組んだ方が楽かもしれない。

一方で、ROMの方はダイオード一本で1ビット出来そうである。もしかしたら、ROMの容量を上げて、RAMの容量は必要最小限に抑えるかもしれない。